I3C接口原理及其应用

2023-08-16

I3C最初的设计目的是为移动设备创建一个能够使用多个传感器的单一接口。随着现代化移动设备对于传感器数量的增加以及对性能的提高,I2C和SPI已经达到了他们所能支持的临界点,而I3C的出现就是为了解决这一问题,I3C可以在同一根主线上支持更多的传感器设备,而且不会因为要支持中断或睡眠模式而增加额外的逻辑信号。I3C可以在更低功耗的情况下提供更快的传输速率,该特性的提升不止是对移动设备,对其他的嵌入式设备也都是很大的帮助。例如穿戴设备,需要在有限的物理空间中使用多个传感器并且要求更小的耗电。

一、简述

I3C(Improved Inter Integrated Circuit)升级版的集成电路总线,同样两根总线:SDA和SCL

I3C接口致力于改善I2C的性能,并提供向后兼容,即兼容I2C。

名词解释:

SDR:Single Data Rate 单一数据传输模式

HDR:High Data Rate 高速数据传输模式

Main Master:当前被配置为I3C总线的主设备

Secondary Master:可以作为I3C的主设备,但是当前被配置为从设备。除了Current Master以外,总线上任何一个具有I3C Master功能的设备

Current Master:此时此刻是主设备

二、连接方式

SDR模式是I3C总线上的默认通讯模式,也是从Current Master向Slave传输私有消息的主要模式。I3C SDR模式与传统的I2C协议非常相似,无论是处理过程还是条件,因此I3C与许多I2C设备可以并存。

那么如何区分是I2C的数据包还是I3C的呢?

三、通讯协议

1、SDR动态分配地址

2、主设备发送的地址

I3C Slave设备不需知道自身处在I2C总线上或是I3C总线上。如果其自身有一个I2C静态地址,那么它可以一直使用这个地址,直到被赋予一个动态地址。一旦被赋予了动态地址,它就必须作为一个I3C Slave设备工作,除非被要求重置。在被赋予动态地址之前,I3C Slave 设备只能以I2C设备的方式工作,但是添加了以下特性:

必要时候紧接着START条件可以响应I3C广播协议。

正确处理CCC的ENTDAA和SETDASA命令。 / AMSS/ sm8250_slpi/ slpi_proc/ ssc/ inc/ utils/ sns_com_port_types.h

3、I3C从设备的职责

紧随START或Repeated START条件,以任何速率尝试对I3C总线上的广播地址或指向自己的地址进行响应。一旦被选中,则I3C Slave就把这一条消息当成SDR模式处理。

如果一条消息指向Slave的动态地址,那么Slave可以ACK或简单NACK这个地址头。

如果ACK,则I3C Slave以SDR模式处理这条消息。

如果NACK,则抛弃接下来的任何数据,等待下一个START或Repeated START。

如果消息是一条广播消息,且读写标识为写,则Slave需要至少处理数据中的头一个字节。

如果广播消息的数据为一个字节,则这则消息为CCC。

I3C Slave 必须处理所有可以应用的CCC命令。一条命令可能是必须的,也可能根据上下文可选的。

如果CCC命令改变了了I3C总线的模式,则I3C Slave必须以下述两种方式中的一种来处理:

如果新的模式为动态地址指定模式,并且请求的是所有I3C Slave,则当前没有动态地址的设备都要参与地址的指定;已经有动态地址的则等待动态地址指定模式的退出。

如果新的模式为HDR,则支持HDR的Slave 可以选择进入HDR,不支持HDR的设备则启动本设备的HDR退出监测器以监听HDR Exit序列的到来。

如果消息的地址头既不是广播也不是动态地址,则I3C Slave必须等待Repeated START 或是 STOP。Slave可以记录或监测总线上传输的位流,但在总线上只能进行等待。

4、公共传输格式

5、特性

I3C允许从设备启动带内中断,这对于I2C和SPI设备来说都需要一根额外的信号线才能实现。当总线处于空闲状态时,从设备可以通过中断机制发送一个"START"信号,然后主设备会为从设备提供一个时钟信号,从设备可以通过主设备提供的分配地址将设备驱动到总线上来启动中断。如果此时有多个从设备尝试启动中断,则地址最小的从设备获得此次仲裁。同时主设备发出ACK信号响应此次中断并重新启动总线或者继续从从设备接收数据,也可以发出NACK信号来结束通信。例如,光传感器通常用于控制设备中显示器背光亮度,如果光条件改变,传感器向系统发出中断,请求发送数据到系统,当光条件稳定时,传感器不需要发送中断和数据,系统也不必查阅传感器数据,从而节约了功耗和实效。

I3C允许从设备在总线配置完成之后再连接到总线上,即热接入特性。连接在同一总线上的传感器可以暂时关闭,直到需要唤醒的时候才激活唤醒。热连接应遵守特定的电气限制,不得干扰MIPI I3C线路。已为启用和禁用事件、管理MIPI I3C特定功能(动态寻址、定时控制等)等标准操作定义了一组通用命令代码(CCCs)。该通用命令代码可以发送广播(发送给所有设备)或者可以指向总线上的特定设备。在使用传感器时功耗和性能是我们必须考虑的,因为即使主程序处理器处于空闲状态(低功耗模式或者深度睡眠),Always-on sensors 和 sensor hubs也会不断的累积数据,累积的传感器数据通常是有规律的,需要在sensor、sensor hub和application processor之间定期快速传输,从而最大限度地降低功耗。

I3C,升级版I2C

I3C作为I2C的升级版,在使用功率和性能方面有重大改进,同时速率也升级到可以替代SPI的中速,相当于SPI 30MHz下的速率。I3C规范的主要制定者包括NXP,Qualcomm,Intel,还有Invensense,TI,STM,Synopsys,Cadence,Mentor,Sony,Knowles,Lattice这些提供助力的厂商。

众所周知I2C是两根线,但是它的中断脚、使能脚等等都要通过GPIO连到SoC上,随着传感器数量的增加,使用I2C只能不断增加GPIO。I3C将这些中断做成了内置,可以帮SoC省去很多GPIO。I3C也是向后兼容I2C,I2C可以平稳地过渡到I3C。这一升级有效助力了智能手机、可穿戴设备、物联网设备、增强现实/虚拟现实和汽车系统实现更多设计创新。

I3C优势与应用场景在哪里

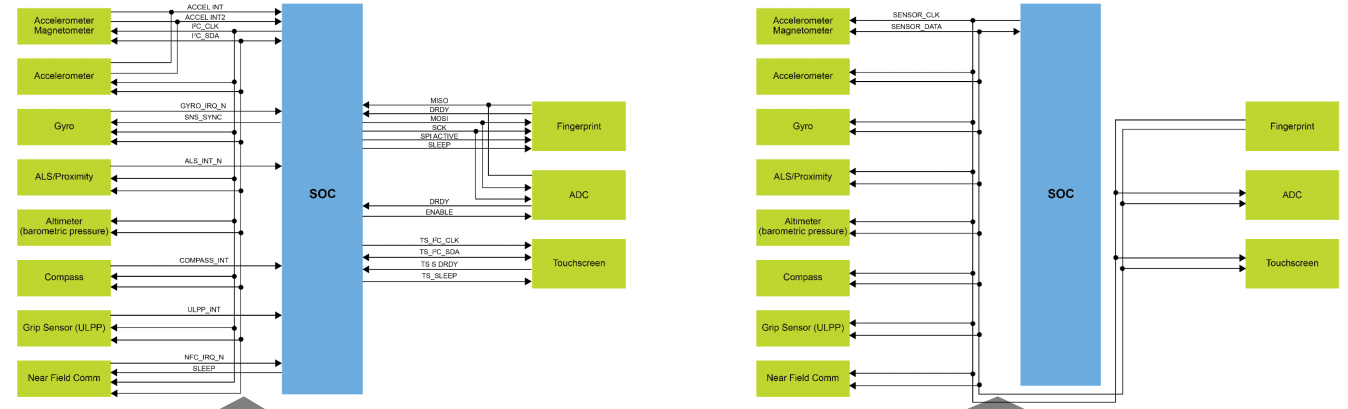

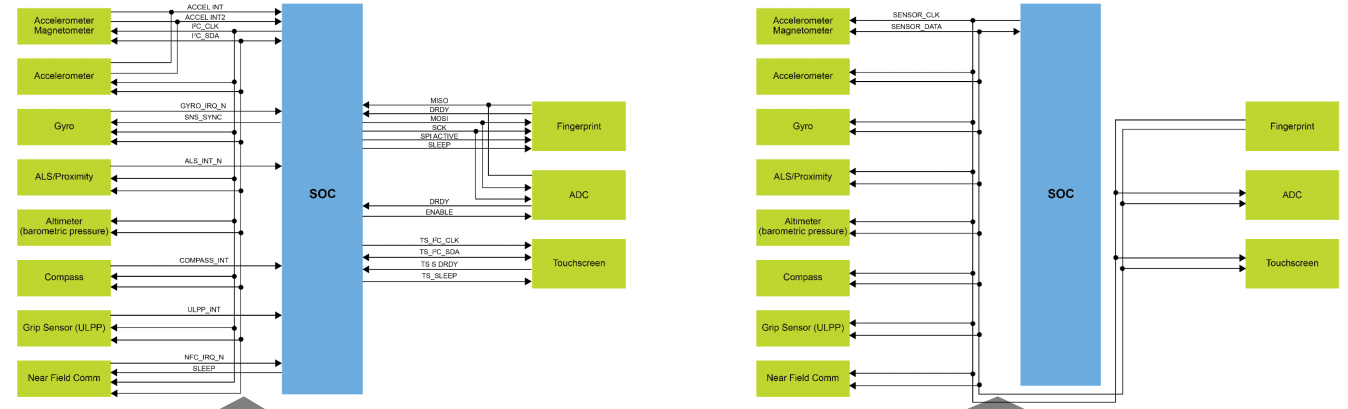

I2C与I3C传感器接口框图对比,NXP

从上图I2C与I3C传感器接口框图对比可以很明显地看到,虽然I2C说是只有时钟线数据线,但是还需要很多额外的从线连到SoC上,GPIO数量的增加以添加SoC包引脚和PCB层计数的形式增加了系统成本,相比之下I3C的布线情况就简洁很多,只需要两根信号线即可,可以显著缩小SoC尺寸。

至于功耗,众所周知I2C的两根线SCL和SDA都是需要接上拉电阻的,上拉电阻的存在导致了I2C功耗会比较大,I3C的SCL全程采用推挽,SDA大部分时间也在推挽模式下工作,因此功耗会降低很大一部分。

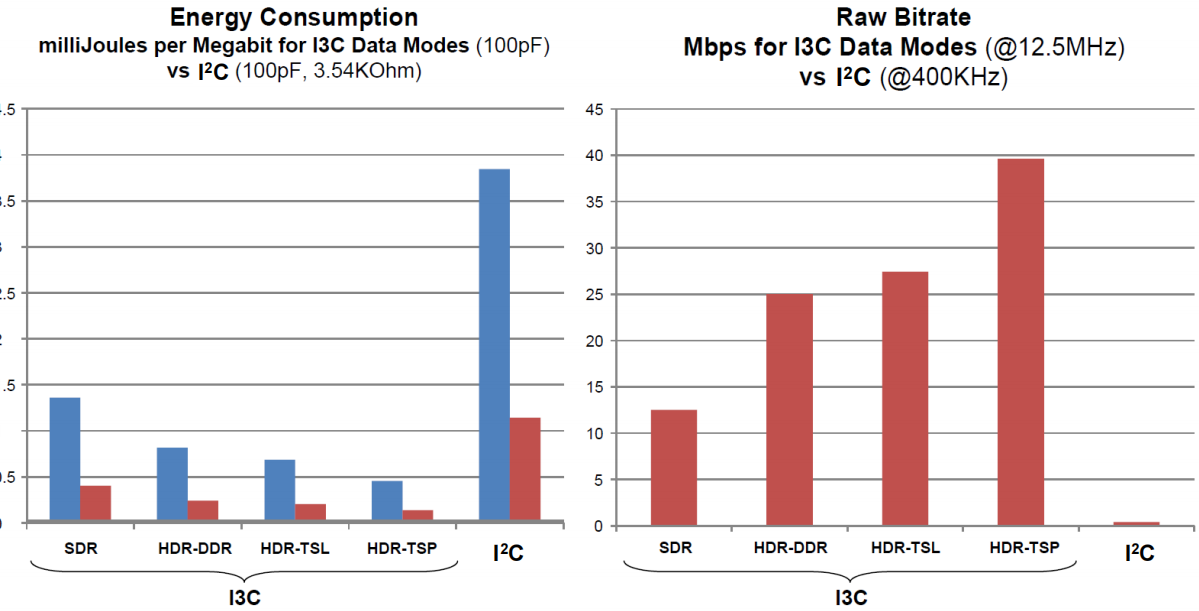

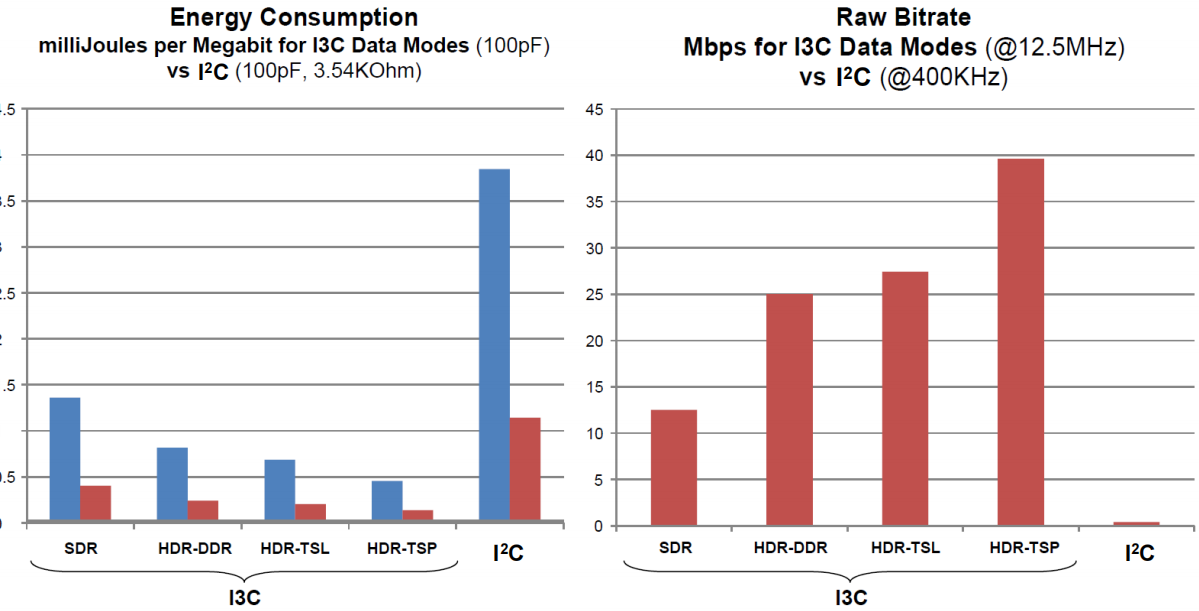

功耗与速率对比,NXP

速率上I2C典型的速率有3 Mbps max at 3.4 MHz (Hs)、0.8 Mbps max at 1 MHz (Fm+)、0.35 Mbps max at 400 KHz (Fm)。I3C典型的数据模式SDR是12MHz下的10.6Mbps,最高速率是HDR模式下的三元采样,达到12.5MHz下的30Mbps。

另外,I2C是没有命令字的,I3C则有着一整套通用命令字的集合。可以通过这些命令字实现动态地址分配、检查当前总线状态、时间控制、IO扩展等等功能。整个功能比I2C有着全面的提升。

从I3C最典型的SDR信号处理上来看,动态地址分配后其启动条件与I2C相同(SCL和SDA从高降到底),但接下来就不同了,I3C SCL可以达到4MHz,并且其高周期<45 ns,比I2C要求的50 ns低得多。接收到ACK之后,主机就会将SDA更改为推挽模式,并将其时钟增加到12.5 MHz使器件进入SDR模式。

地址仲裁可以说是I3C极为重要的特性。上面提到,I3C将中断内置(IBI)进来了,当Slave产生中断时,IBI就会主动向主机发送中断信息,上传地址与其他信息。多个Slave同时产生中断,这时候就有多个地址信息,就需要进行地址仲裁判别优先级。地址仲裁遵从一个原则,那就是0s优先,哪个Slave小哪个优先级更高。地址冲裁也对热插拔、动态地址分配以及多主机申请判别同样有效。

I3C规范的更新

I3C协议V1.1.1的两部分(MIPI会员版和基本版)均是在在去年发布。在最新的V1.1.1版本中,Slave增加了Reset机制,简单来讲就是使用退出HDR模式的方法增强了协议的故障恢复能力。

其次,增加了Group的寻址方式,可以对多个Slave进行分组然后进行寻址,类似于PMBus;再者是引入了HDR-BT模式,以12.5MHz提供高达97Mbps的数据速率;对于DDR模式则增加了Slave的中止、CRC功能;另外,Device-to-device tunnel机制也加入进来,实现Slave之间的直接通信。

I3C厂商动向

NXP

NXP作为I3C协议的主要制定者,提供IP与Silvaco合作,提供Free Basic Slave、Standard Slave、Advanced Slave以及主机四种不同包装的I3C产品,根据不同具体应用的区别,可以为Slave模块添加1.5K到2.5K的门,消耗的功率也很小,并支持采用时钟门控和其他方法来限制功耗。其后端可以在没有系统时钟的情况下运行。在NXP的RT系列MCU中,也可以看到I3C的身影。

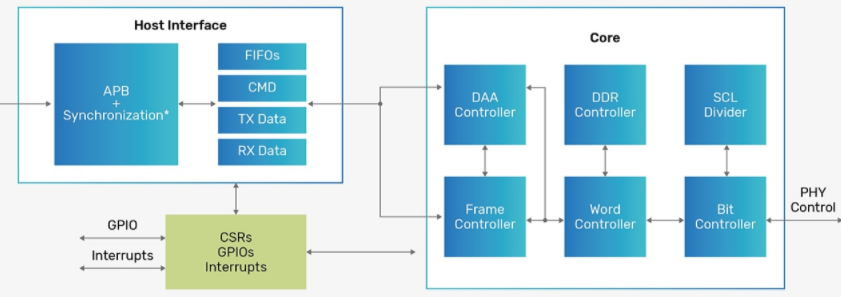

Synopsys

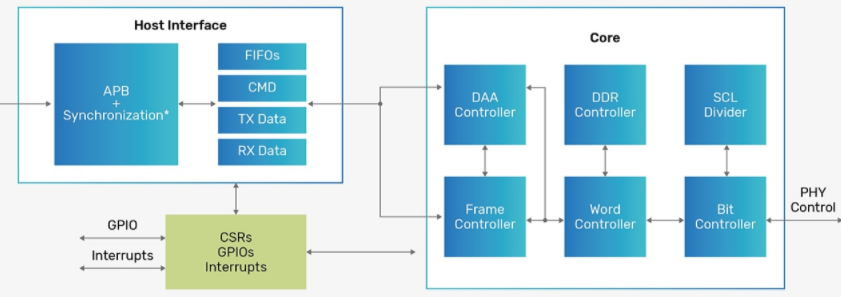

Synopsys也发布了DesignWare MIPI I3C控制器IP,可以将更多传感器集成到系统中,同时简化电路板设计并降低总体成本和功耗。DesignWare MIPI I3C控制器IP多主机操作和32位ARM AMBA 高级外设总线(APB)从接口。基于标准的APB接口将IP连接到SoC的其余部分,同时总线连接到寄存器和直接存储器访问(DMA)接口,从而实现轻松的IP集成,使设计人员能够拥有完整的传感器接口解决方案。

Cadence

作为联盟成员Cadence可以提供MIPI I3C控制器。适用于MIPI I3C的Cadence控制器IP符合MIPI I3C规范,并与I2C规范兼容,其设计可快速轻松地集成到任何移动嵌入式SoC设备中,并以更好的性能和电源效率扩展传感器通信能力。MIPI I3C控制器具有成为I3C总线上的启动器/主机或目标的能力。

Cadence

瑞萨电子

今年,瑞萨电子与Intel联手推出了面向下一代服务器主板和其他基础设施设备的I3C智能开关器件RG3MxxB12系列,为机架内的每个子系统带来先进的平台管理功能。I3C智能开关产品家族允许以最大速度将两个发起设备(上行)端口扩展到四个、八个或更多的目标端口,是MIPI I3C基础应用很好的用例。

瑞萨电子

TI

随着系统中目标设备数量的增加,主机控制器必须考虑减少延迟、实现关键警报功能以及降低通信期间的功耗。TI在今年推出了基于I3C的温度传感器TMP139,以解决DDR5 DIMM等复杂系统中的低延迟热传感挑战。在I3C的助力下,TMP139温度精度超过了规范要求,可实现更高性能的DDR5存储器模块。

TI